|

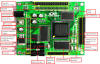

CYCLONE IV EP4CE30 VER3.0 NIOS2 SOPC高速数据采集乒乓算法FPGA开发板

售价:580(元)

一、简介

EP4CE30F23C8N这款芯片采用经过优化的60-nm低功耗工艺,Cyclone IVE FPGA拓展了前一代Cyclone III FPGA的低功耗优势。 新一代器件降低了内核电压,与前一代产品相比,总功耗降低了25%。

核心板板采用是六层PCB设计,采用大容量管脚更多的BGA封装,F484封装,使整个核心板的性能和稳定性有了很大的提供,并同时为用户提供大量的有效I/O(独立I/O一共是157个)。

由于FPGA与存储器直接进行高速数据交换。所以成在很多干扰因素,因此这也是很多

开发板速度很难提高的关键原因。所以我们在设计的时候尽量靠近FPGA芯片。这样就 大限度减少因为布板所造成的干扰因素。

我们的开发板的2个独立的的SDRAM和SRAM都采用独立的数据地址总线进行控制。这样就为使用者提供了更加方面灵活的设计途径

,2个独立的SDRAM可以方便的做高速的数据处理的乒乓算法控制,或一个SDRAM做NIOS的程序存储,另外一个做高速的DMA的数据存储, 高速度可以到166M.

由于布线合理。这块开发板的NIOS能够稳定高速运行在100M频率以上。是您做系统评估或直接兼容 终应用产品 选择。

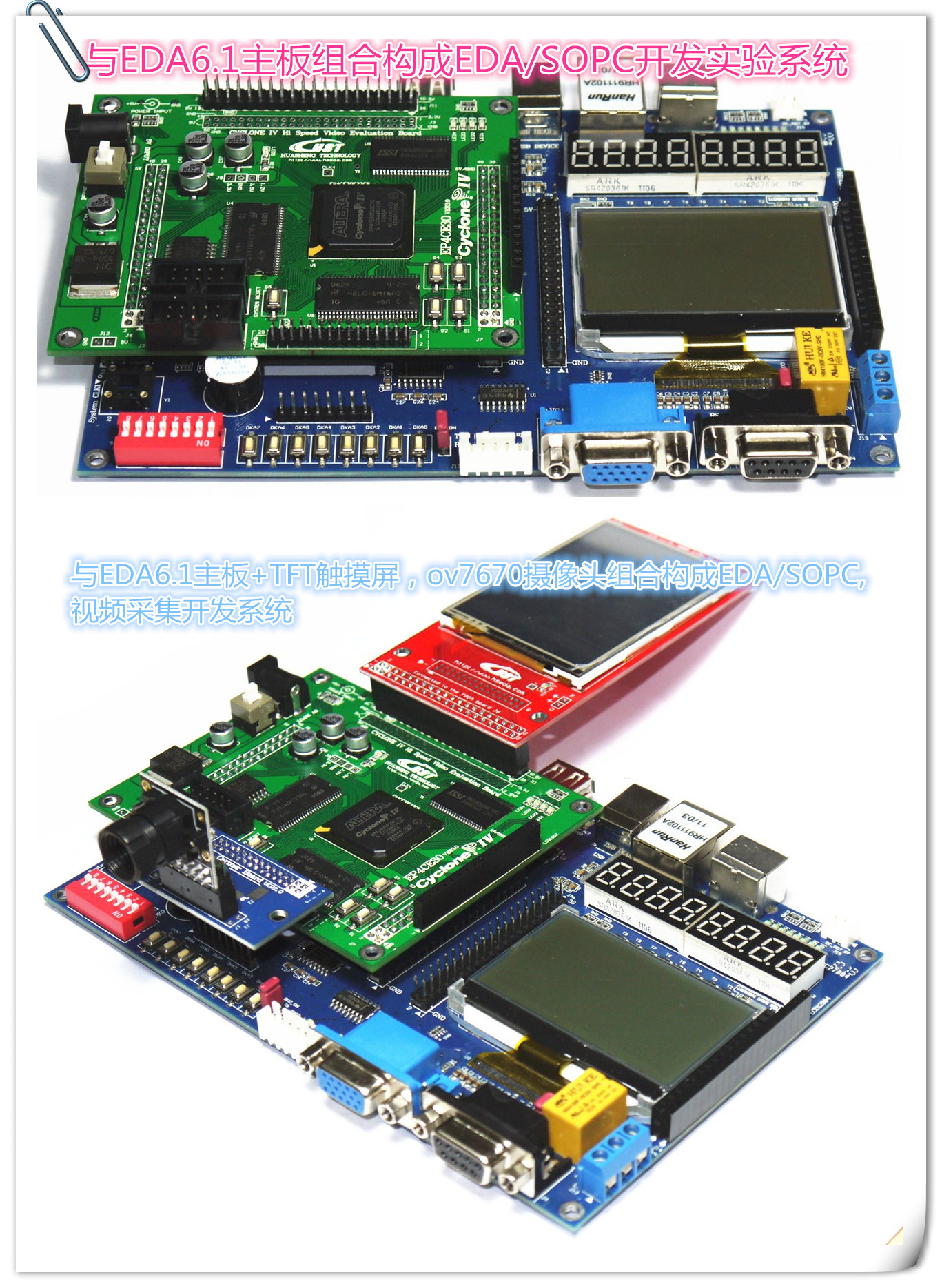

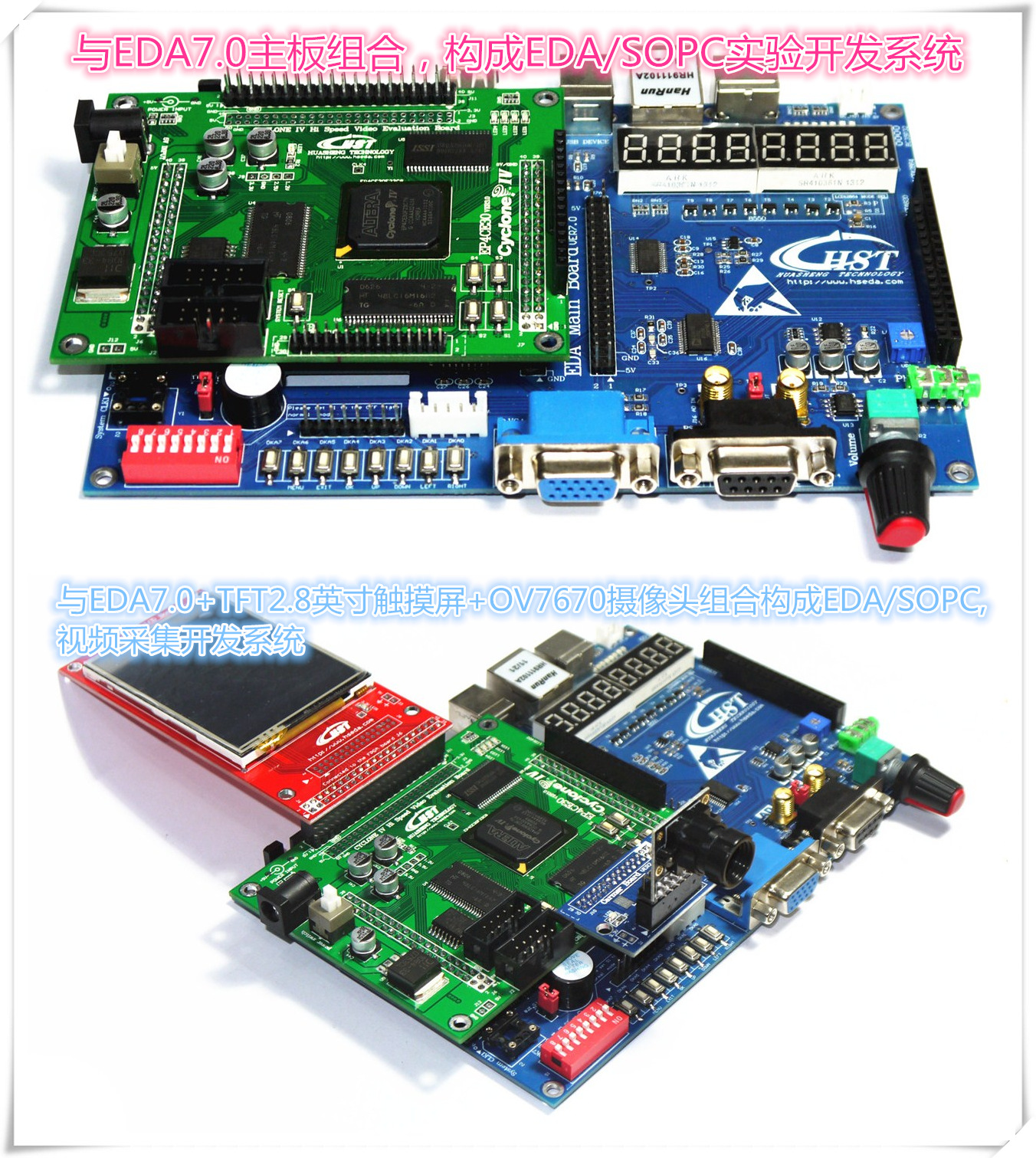

用户如果觉得自己做目标板麻烦。可以购买我们提供的多种扩展板。(本公司有各种视频采集,输出扩展板)或是通过J6,J7直接插到我们的EDA底板上(EDA4.1,EDA5.1,EDA6.1,EDA7.0四种不同可选择主板)或是EDA试验箱上。这样就可以充分利用我们的EDA底板提供的功能多样,完善外设资源。这样就能轻易的构成一套售价低廉,功能 大的SOPC开发,评估系统。

系统结构图

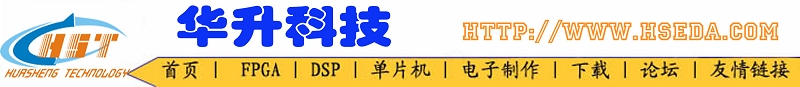

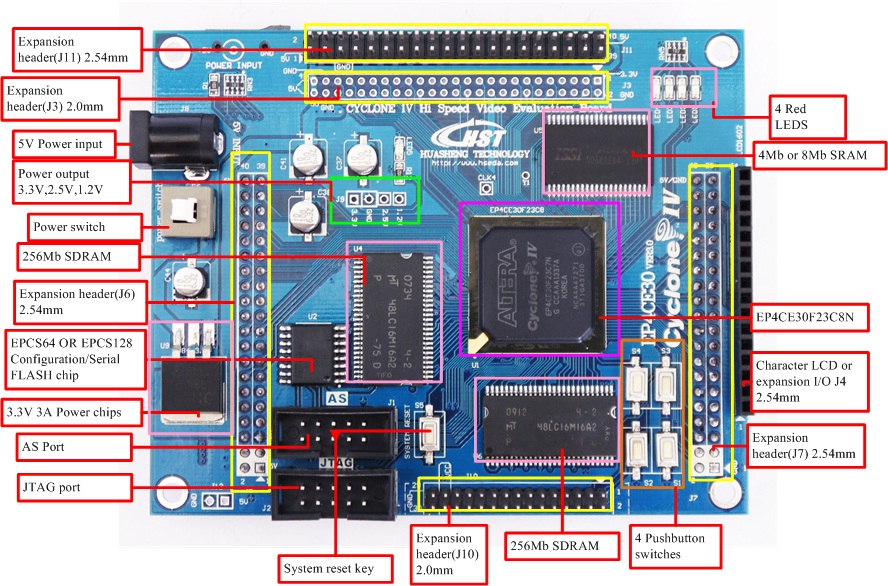

核心板顶层布局图

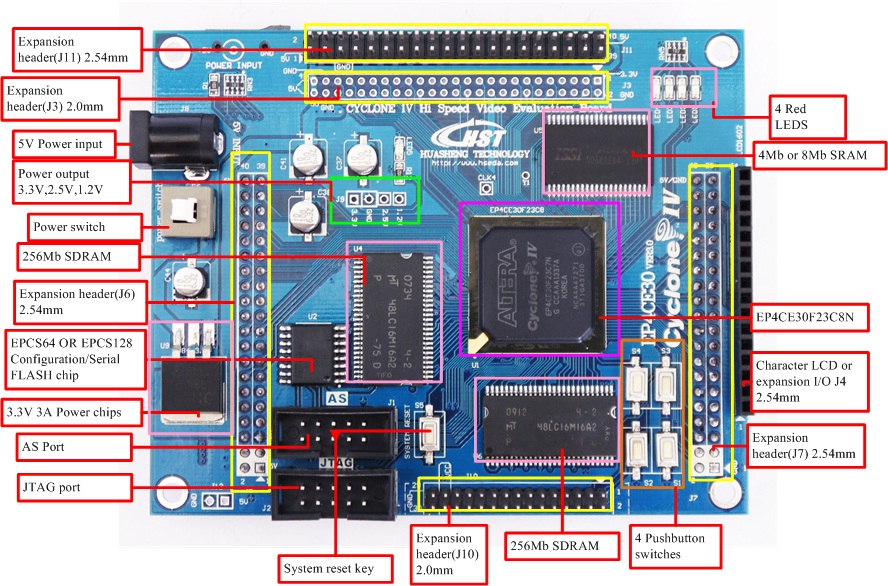

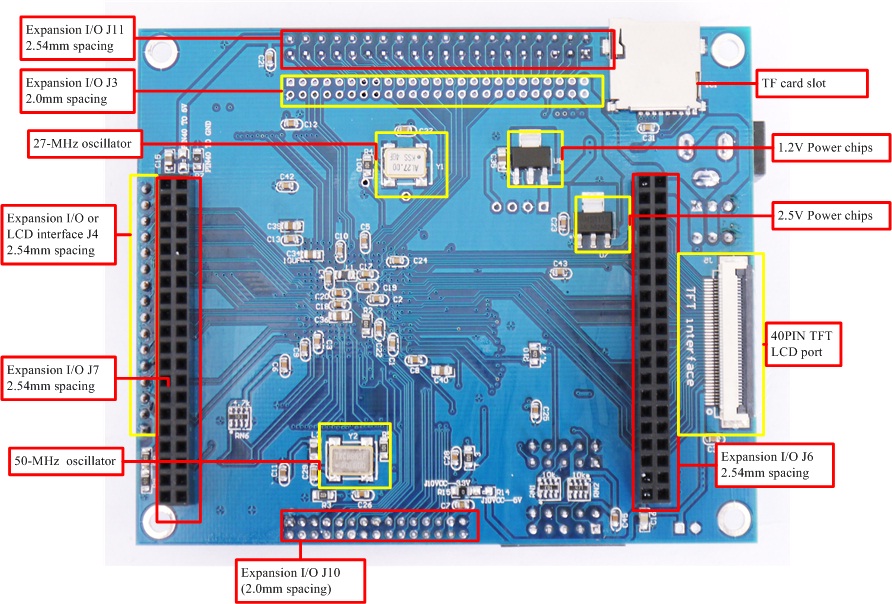

核心板底面布局图

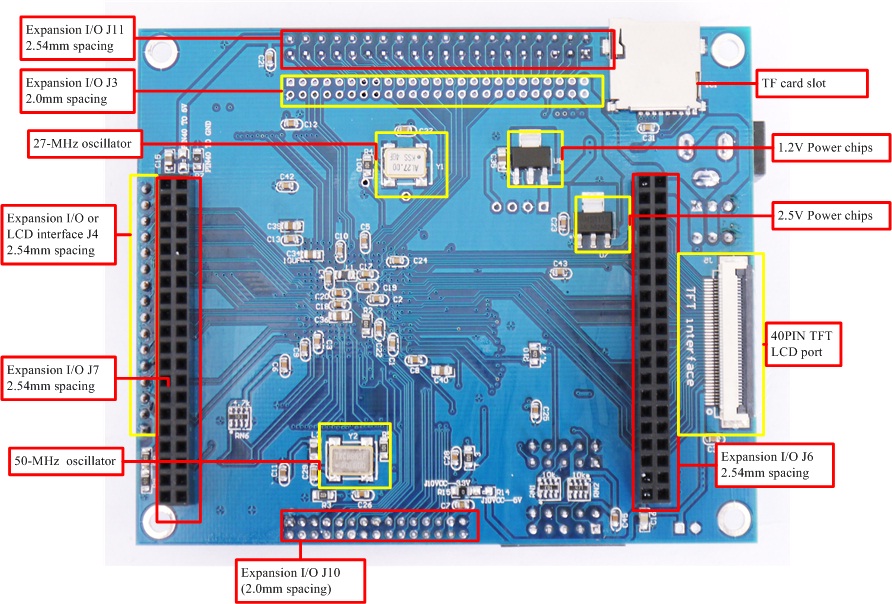

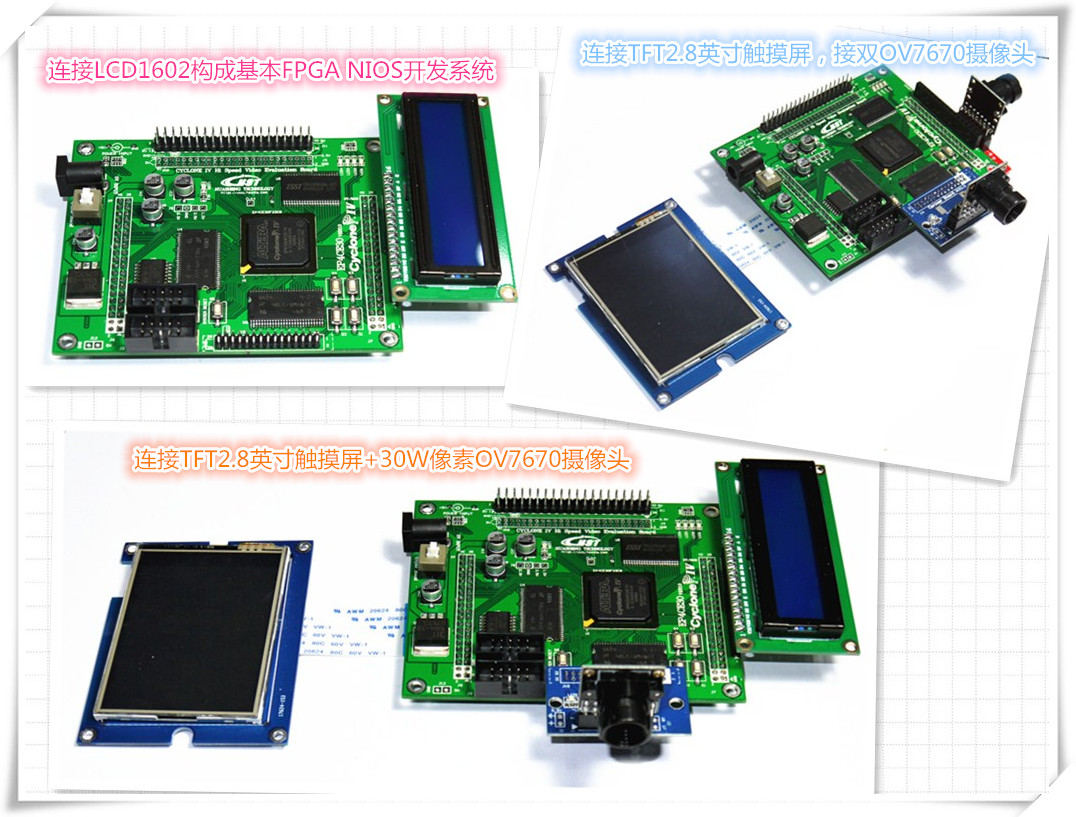

FPGA核心板与TFT LCD接口

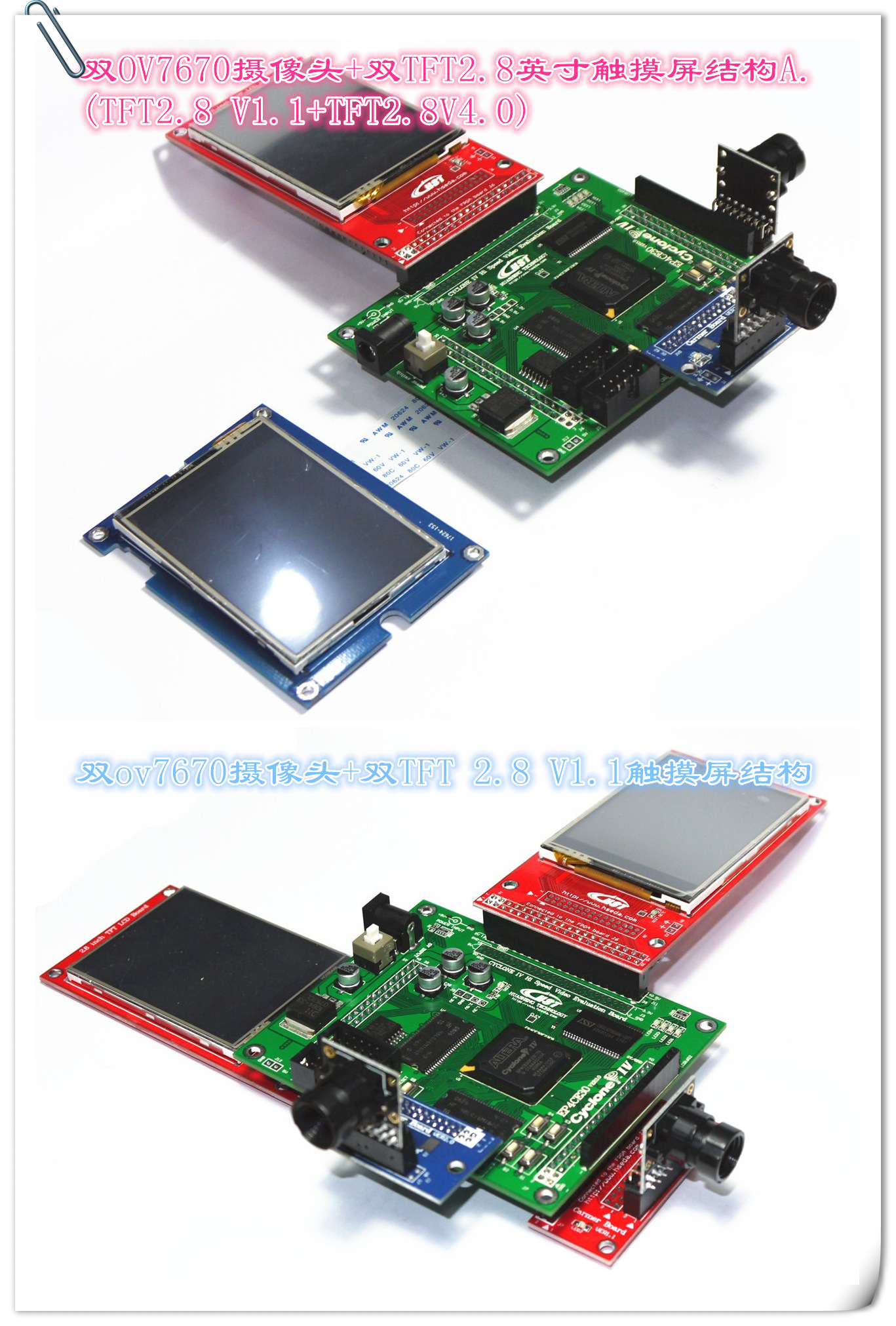

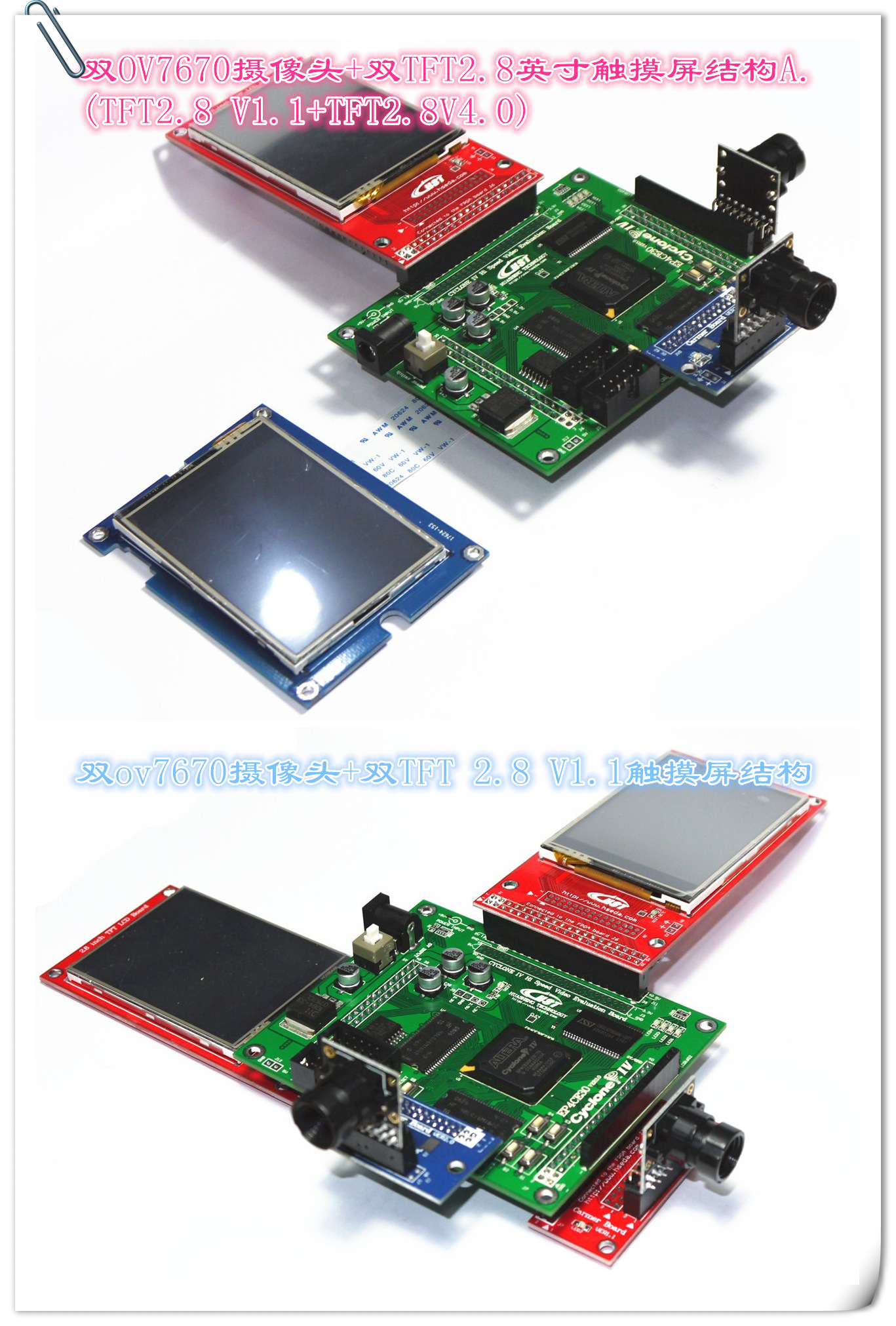

双OV7670摄像头加双TFT2.8英寸触摸屏组合结构图

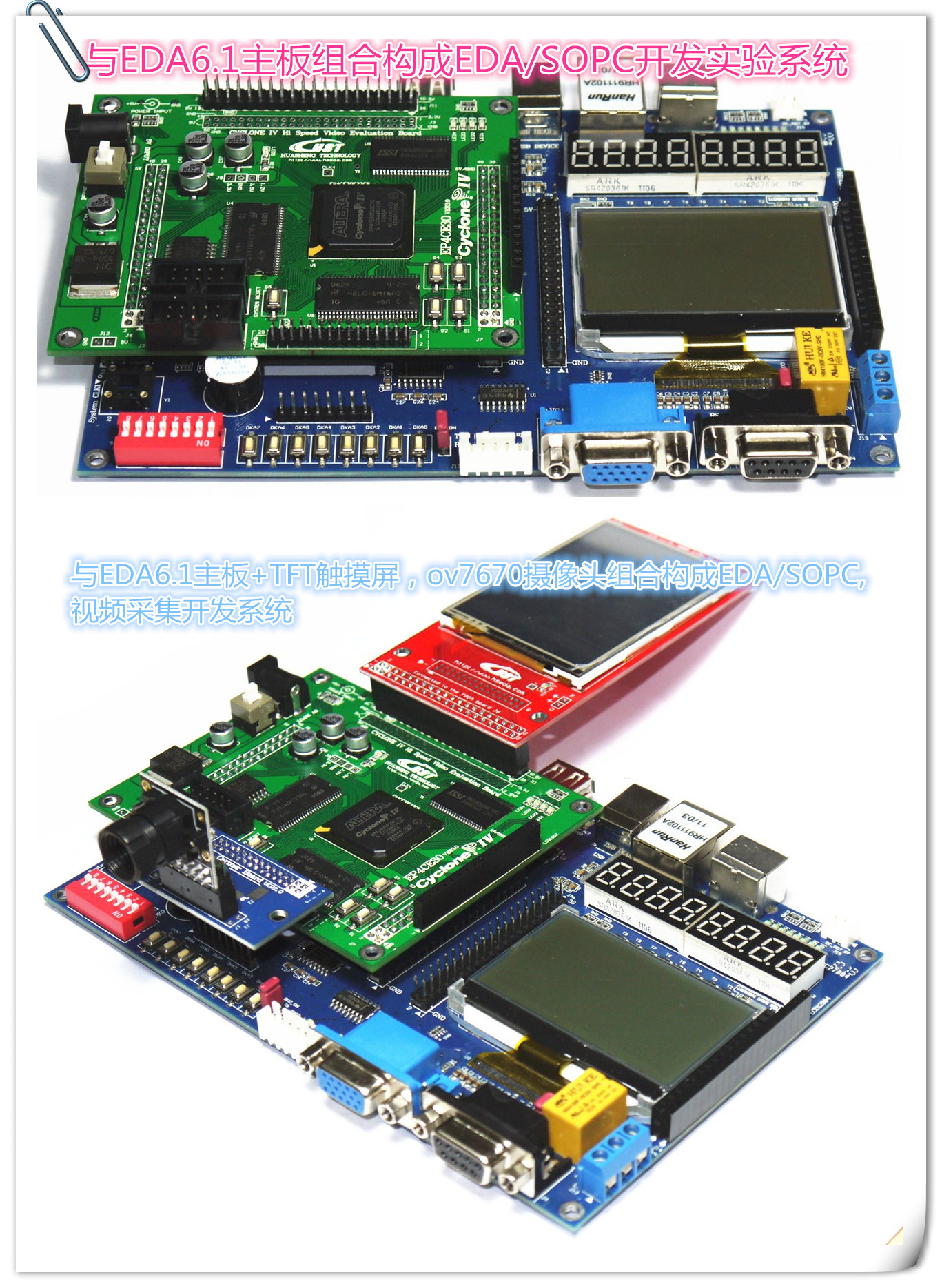

与EDA6.1主板组合成EDA/SOPC开发实验系统

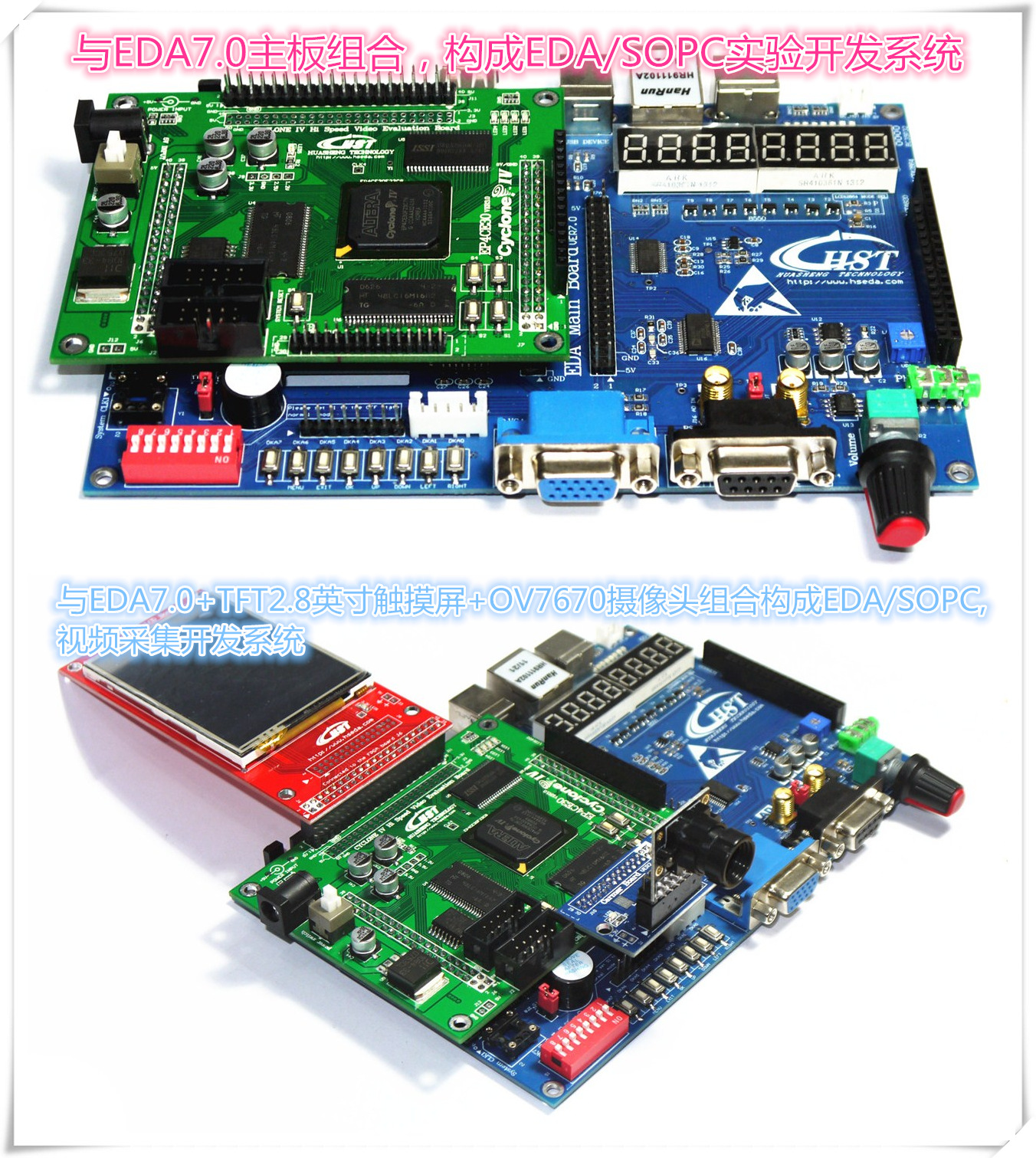

与EDA7.0主板组合成EDA/SOPC开发实验系统

核心板搭载OV7670摄像头+TFT2.8英寸触摸屏+(USB/NET/TFT7INCH)扩展板

二.系统资源

| |

HSEP4CE30 VER3.0 CycloneIV FPGA核心板资源 |

|

编号 |

外设 |

数量 |

说明 |

|

1 |

FPGA芯片 |

1 |

EP4CE30F23C8N(FBGA484封装),Speed Grade 8,Logic

Elements 28848,Memory Bits 608256,Embedded

Multipliers 132,Global Clocks 20,I/O 533,PLLs 4 |

|

2 |

PCB布线 |

|

高速6层PCB布线,资深工程师手工布线,并进行EMC仿真分析,从而保证系统高速运行。 |

|

3 |

串行FLASH |

1 |

标配EPCS64(64Mbit),选配EPCS128(128Mbit),烧写固件或NIOS程序以及用户数据。 |

|

4 |

SRAM |

1 |

标准配置一片256K×16Bit SRAM

(4Mbit),独立地址数据总线方便使用,可选配512K x

16bit(8Mbit),高速静态SRAM 10ns读写 |

|

5 |

SDRAM |

2 |

二片16M×16Bit SDRAM , 高166MHz读写速度

256Mb,超大容量,我们已经预留了扩展I/O,可以直接扩展到32M X 16bit SDRAM

(64M byte). 独立I/O控制,2片SDRAM都是独立数据地址总线,可以实现图像采集的乒乓算法。 |

|

6 |

TF/SD卡座 |

1 |

提供一个标准的TF卡插槽,支持FAT16,FAT32数据格式存储 |

|

7 |

时钟 |

2 |

2个源时钟50M,27M方便用户使用和分频处理,用户可以自行更换其他频率 |

|

8 |

LCD |

1 |

一个标准LCD1602液晶接口,NIOS IP核直接支持。独立I/0,也可以做用户I/O |

|

9 |

TFT LCD接口 |

1 |

提供一个标准的40PIN的TFT

LCD2.8英寸触摸屏的接口。可以直接连接我们的TFT2.8英寸触屏 |

|

10 |

琴键开关 |

4 |

带上拉电位,用户按键输入。 |

|

11 |

RS232 |

1 |

标准RS232接口,MAX232芯片接口转换 |

|

12 |

电源 |

3 |

5V,3.3V/3A,1.2V/800MA,2.5V/800MA,独立引出方便用户使用和测试 |

|

13 |

JTAG端口 |

1 |

在线调试FPGA,NIOS读写FLASH,固化用户程序和固件 |

|

14 |

AS端口 |

1 |

EPCS串行FLASH编程烧写 |

|

15 |

LED |

4 |

独立I/O |

|

16 |

系统主复位 |

1 |

系统复位按键,带上拉。也可以做为用户按键输入。 |

|

17 |

扩展I/O |

6 |

(J6)38+(J7)38+(J10)26+(J4)11+(J3)44=157个(引出独立I/O) |

EP4CE30电子相册实验

http://v.youku.com/v_show/id_XNjYyODcyMDA4.html

核心板与摄像头和TFT2.8英寸触摸屏接口,构成完整SPOC视频开发系统(实时采集回放实验)

http://v.youku.com/v_show/id_XNjYyODczMjM2.html

http://v.youku.com/v_show/id_XNjYyODc0MDU2.html

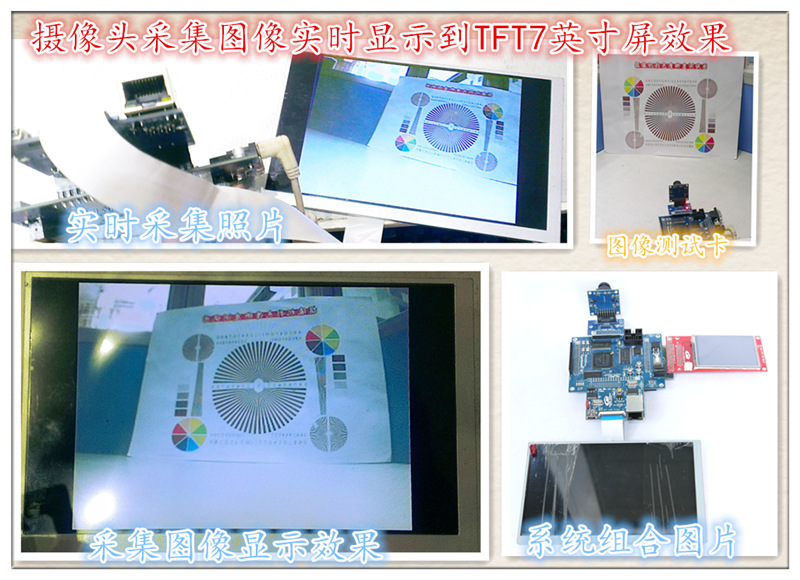

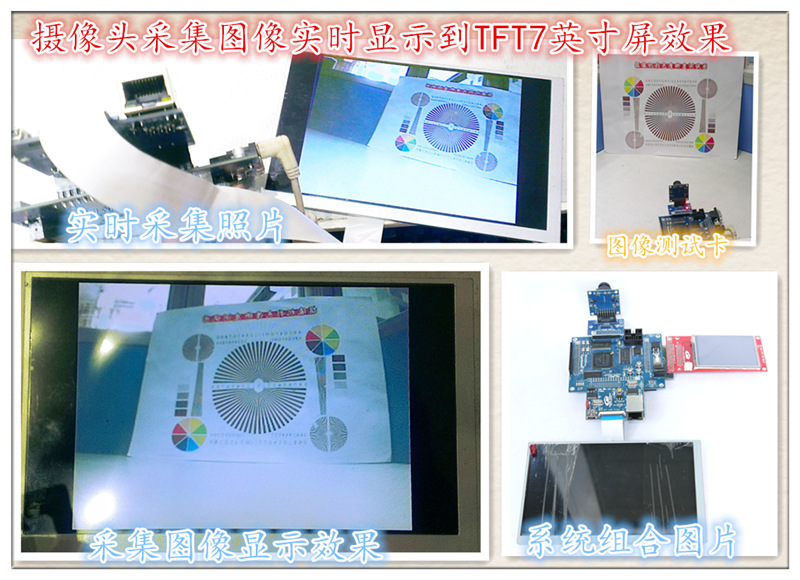

摄像头采集到7英寸TFT屏显示实验(VERILOG代码)

(搭载NET+TFT7INCH+USB扩展板)

TFT2.8英寸触摸屏加蓝牙模块 VER4.0

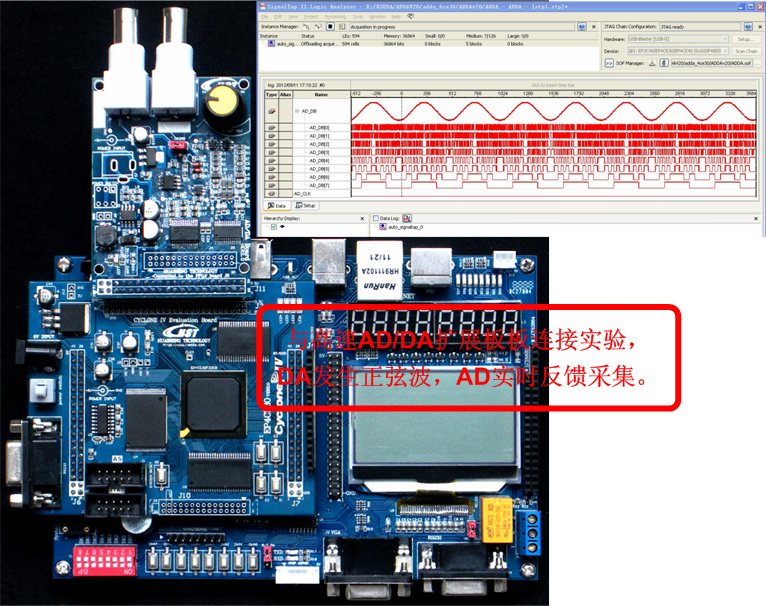

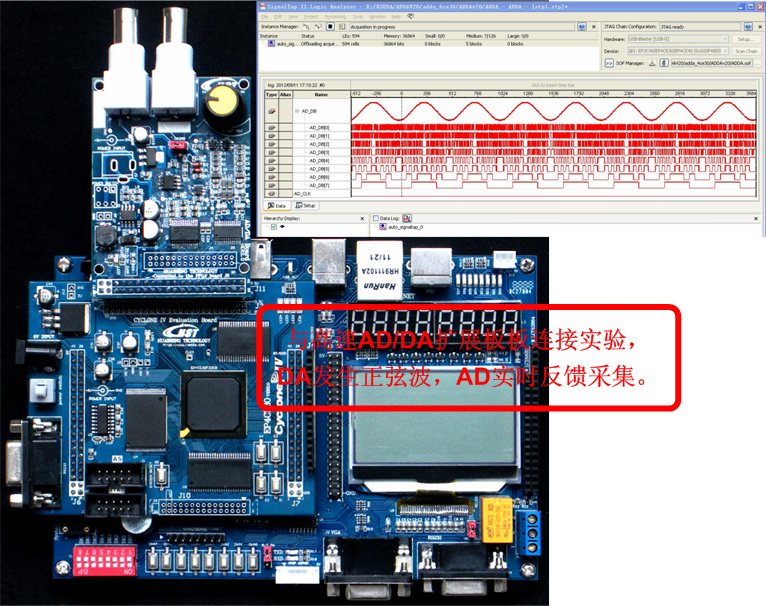

高速AD/DA实时采集回放实验(DA发生输出正弦波,AD实时采集)

实验视频地址:http://v.youku.com/v_show/id_XNDU5NTc4NjAw.html

三:

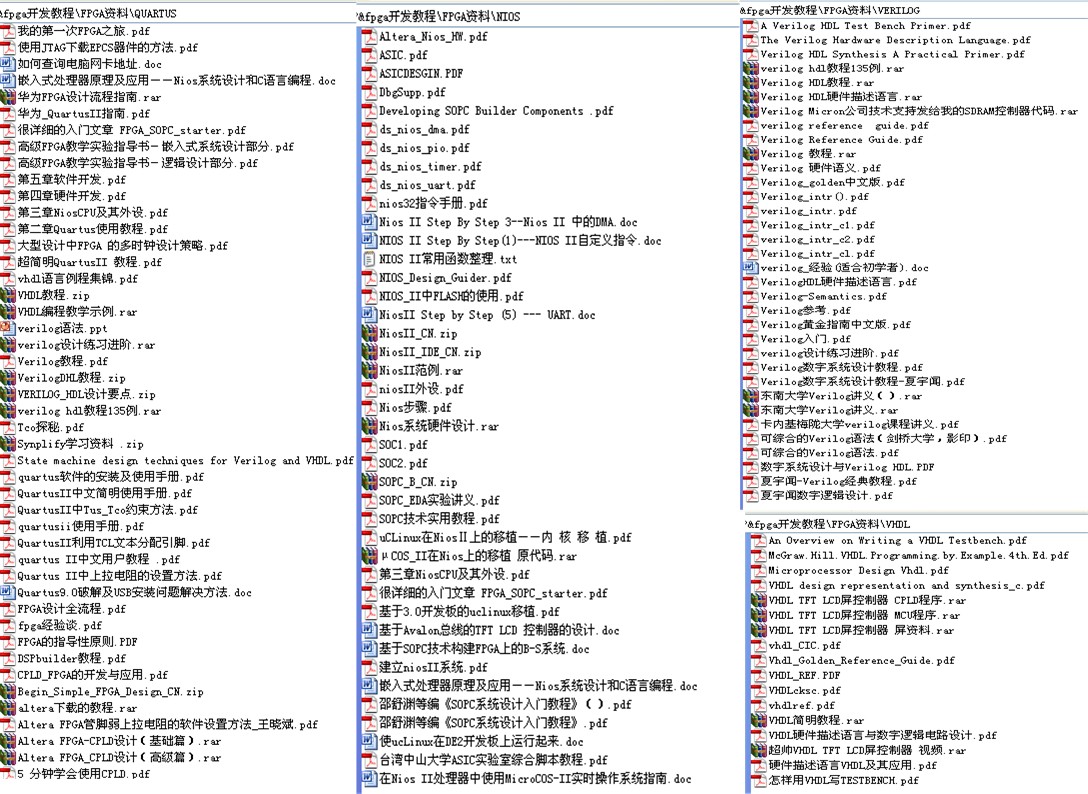

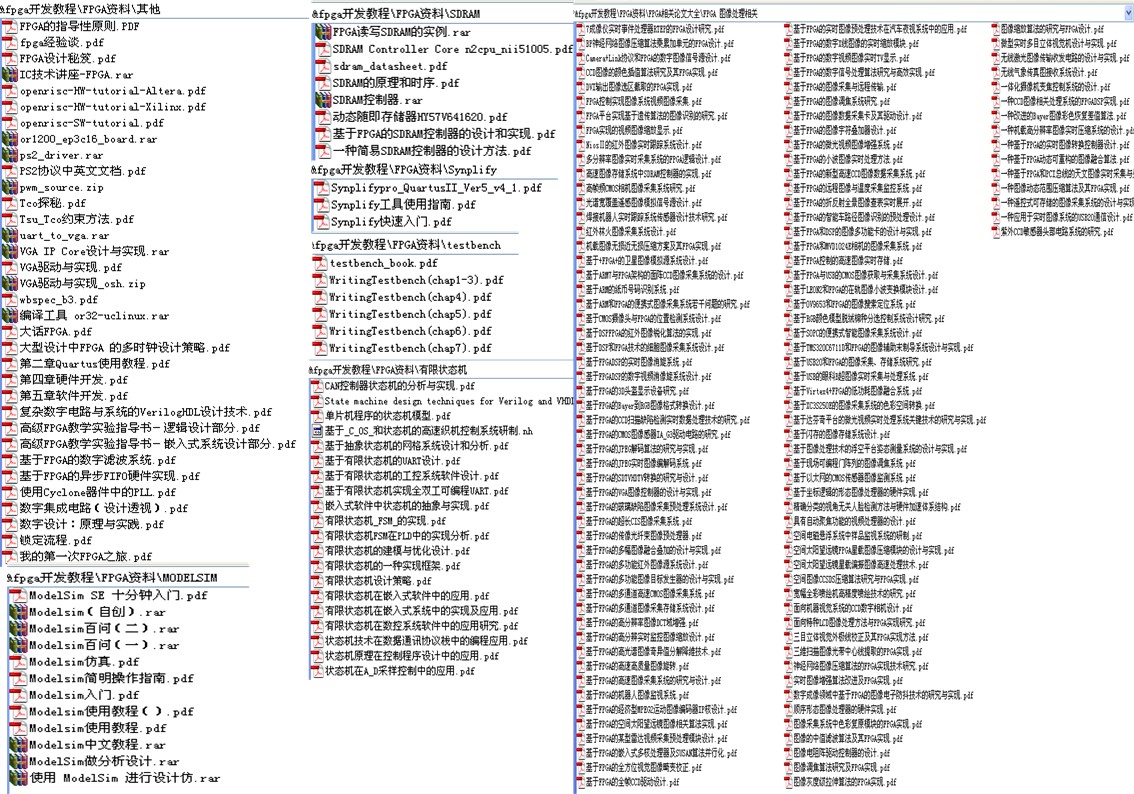

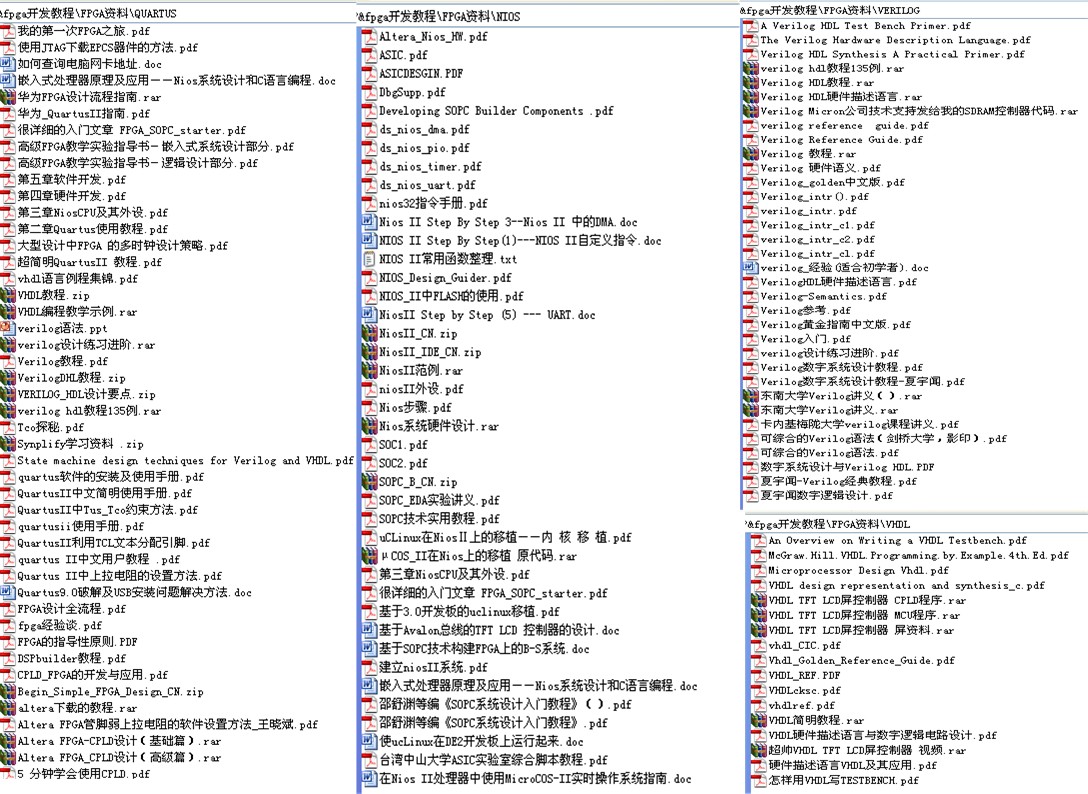

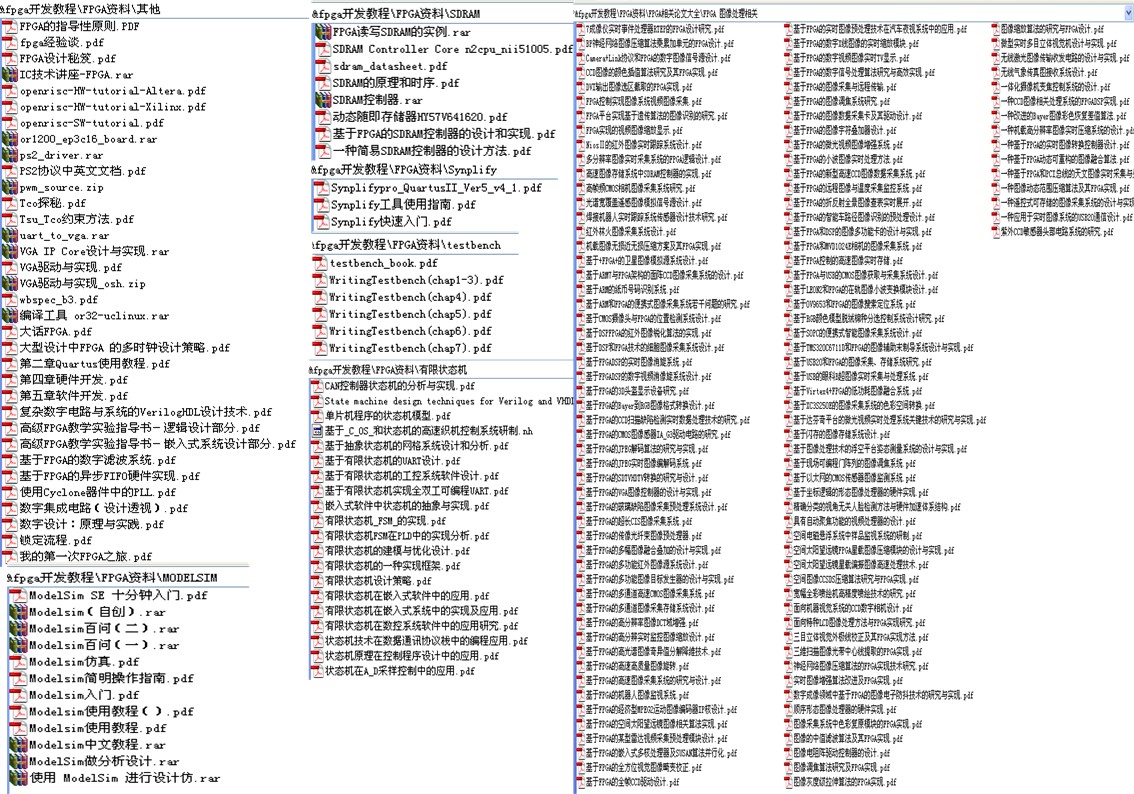

配套资料

开发系统配套了3张DVD光盘,里面包含了原理图,源代码,原创教程,

以及大量视频教程等等。

配套的FPGA开发软件为:

Quartus II 11.0sp1

NIOS II IDE 11.0sp1

ModelSim 10.0c SE

大量教程教程让您轻松上手

四.实验代码

|

EP4CE30 SOPC开发系统例程清单

(这部分代码要配合对应的EDA6.1底板使用) |

|

EDA实验 |

|

SOPC (NIOS II)实验 |

|

编号 |

实验例程 |

|

编号 |

实验例程 |

|

1 |

3/8 译码器 |

|

1 |

hello实验 |

|

2 |

分频器(VERILOG) |

|

2 |

LED流水灯实验 |

|

3 |

BCD 七段显示译码器实验 |

|

3 |

中断实验 |

|

4 |

4X4矩阵键盘实验 |

|

4 |

串口通信实验 |

|

5 |

6分配实验(VHDL) |

|

5 |

RTC控制实验 |

|

6 |

四位加法器 |

|

6 |

IIC EEPROM读写实验 |

|

7 |

多路选择器 |

|

7 |

SPI实验 |

|

8 |

十六进制BCD译码器 |

|

8 |

网络通信实验 |

|

9 |

简易频率计 |

|

9 |

系统时钟实验 |

|

10 |

比较器 |

|

10 |

定时器实验 |

|

11 |

并口转串口简易控制器 |

|

11 |

PS2键盘实验 |

|

12 |

异步清零加法计数器 |

|

12 |

DMA实验 |

|

13 |

移位运算器 |

|

13 |

SDRAM读写实验 |

|

14 |

LPM_ROM |

|

14 |

串行FLASH读写实验 |

|

15 |

LPM_RAM |

|

15 |

12864(ST7565)液晶显示实验 |

|

16 |

数字时钟 |

|

16 |

PWM实验 |

|

17 |

流水灯实验 |

|

17 |

LCD1602显示实验 |

|

18 |

RS-232 串口控制器 |

|

18 |

USB通信实验 |

|

19 |

LCD1602液晶驱动显示实验 |

|

19 |

U盘读写实验 |

|

20 |

VGA 控制输出实验 |

|

20 |

SD卡读写控制实验 |

|

21 |

在VGA显示器上显示字母和图像 |

|

21 |

AVALON IP核实验 |

|

22 |

PS/2 键盘控制器实验 |

|

22 |

数码管显示实验 |

|

23 |

接口互连实验 |

|

23 |

LCD2864(ST7920)显示实验 |

|

24 |

音乐演奏实验 |

|

24 |

NIOS固化到串行FLASH实验(EPCS) |

|

25 |

红外遥控实验 |

|

25 |

NIOS固化到并行FLASH实验(AM29LV128) |

|

26 |

步进电机控制实验 |

|

26 |

系统全检测实验 |

|

27 |

直流电机速度控制和闭环测速实验(PWM) |

|

|

|

|

28 |

LCD12864动画显示实验(ST7565P) |

|

|

|

|

29 |

DS1302实验 |

|

|

|

|

30 |

LCD12864汉字中文显示实验(VERILOG) |

|

|

|

|

31 |

LCD12864汉字中文显示实验(VHDL) |

|

|

|

五.相关配置

|

标准配置发货清单 |

|

EP4CE30 V3.0核心板一块 |

LCD1602液晶一个 |

5V/1A开关电源一个 |

DVD2张 |

|

六.配件清单 (标准配件)

-

EP4CE30 VER3.0核心板 一块

-

5V/1A开关电源 1个

-

LCD1602液晶 1个

-

资料光盘 DVD光盘 2张

七.可选配件

-

2.8英寸TFT 触摸屏VER1.1 100(元)

-

2.8英寸TFT 触摸屏VER4.0 110(元)

-

30万像素摄像数字头 100(元)

-

USB+网络+TFT7英寸屏扩展板 90(元)

(原件180元)

-

USB BLASTER下载线(ALTERA原厂方案) 70元 (原件90元)

-

USB BLASTER Ver.C下载线

40(元)

-

音频视频采集开发板VIDEO3.1 350元

-

音频采集SD/CF卡扩展板 150元

-

LCD12864液晶(带中文字库) 65元

-

EDA4.1主板 200(元)

-

EDA5.1主板 800(元)

-

EDA6.1主板 200 (元)

-

EDA7.0底板 260(元)

-

USB2.0 VGA/SD卡 扩展板 130(元)

-

高速AD/DA模块

VER2.0 90(元) (原件130元)

-

AD/DA模块

VER1.0 70(元)

-

24bitAD/高速DA扩展板模块

130(元)

|