|

||||||||||||||||||||||||||||||||||

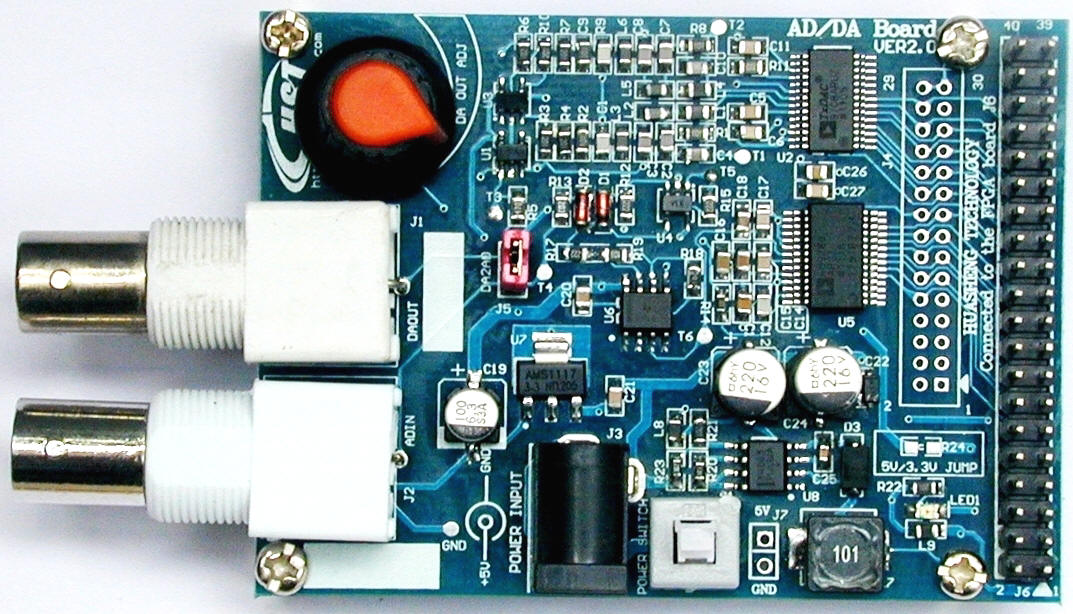

高速AD/DA模块 VER2.0零售价(180元) FPGA核心板配板价格(120元) 一、 产品图片

二、 产品可以配合的核心板列表感谢您选购由武汉华升泰克电子技术有限公司推出的高速AD/DA模块,此模块需要与其他开发板配合使用,支持FPGA开发板列表如下

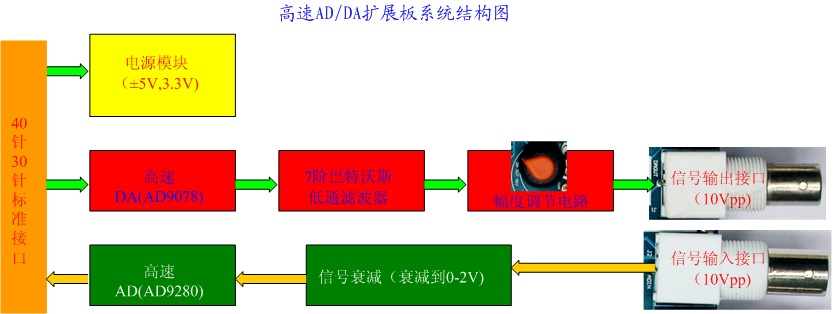

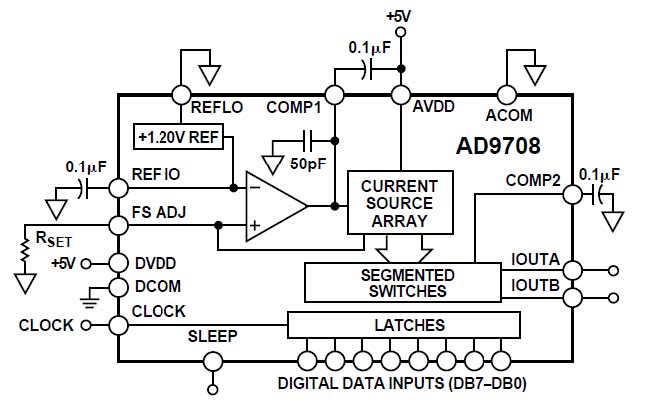

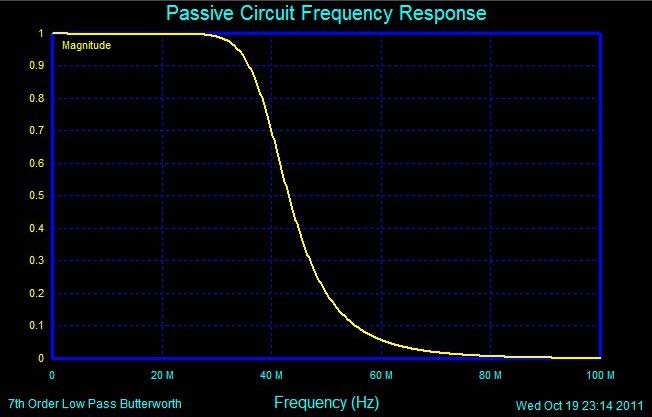

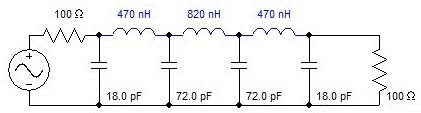

后续支持硬件将通过武汉华升泰克电子技术有限公司更新。 三、 硬件结构 四、 数模转换(DA)电路如硬件结构图所示,DA电路由高速DA芯片、7阶巴特沃斯低通滤波器、幅度调节电路和信号输出接口组成。 我们使用的高速DA芯片是AD公司推出的AD9708。AD9708是8位,125MSPS的DA转换芯片,内置1.2V参考电压,差分电流输出。芯片内部结构图如下图所示 AD9708芯片差分输出以后,为了防止噪声干扰,电路中接入了7阶巴特沃斯低通滤波器,带宽为40MHz,频率响应如下图所示

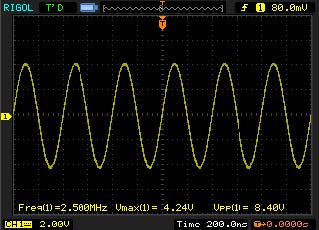

滤波器参数如下图所示 滤波器之后,我们使用了2片高性能145MHz带宽的运放AD8056,实现差分变单端,以及幅度调节等功能,使整个电路性能得到了 大限度的提升。幅度调节,使用的是5K的电位器, 终的输出范围是-5V~5V(10Vpp)。 注:由于电路器的精度不是很 , 终的输出有一定误差,有可能波形幅度不能达到10Vpp,也有可能出现波形削顶等问题,这些都属正常情况。 五、 波形展示

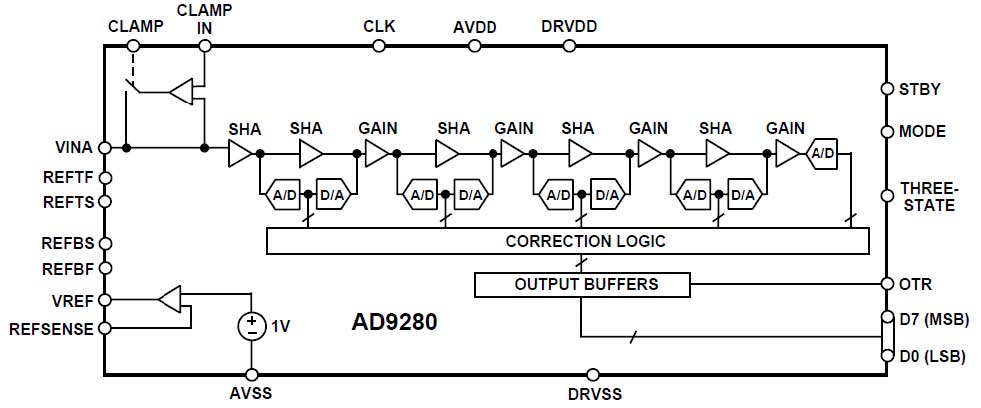

注:由于幅频特性的影响,随着频率的增加,波形的幅度会不断减小。 六、 模数转换(AD)电路如硬件结构图中所示,AD电路由高速AD芯片、衰减电路和信号输入接口组成。 我们使用的高速AD芯片是由AD公司推出的8位, 大采样率32MSPS的AD9280芯片。内部结构图如下图所示

根据下图的配置,我们将AD电压输入范围设置为:0V~2V

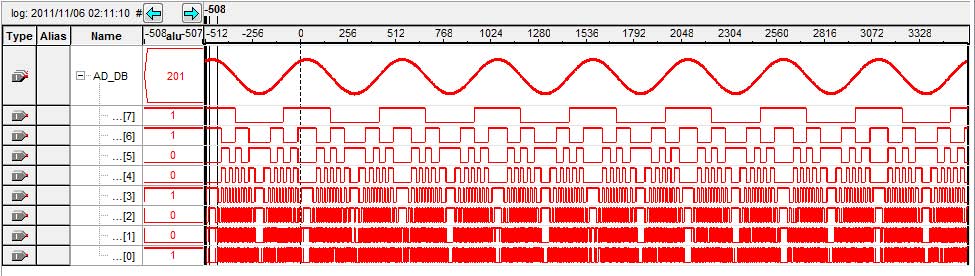

在信号进入AD芯片之前,我们用一片AD8056芯片构建了衰减电路,接口的输入范围是-5V~+5V(10Vpp)。衰减以后,输入范围满足AD芯片的输入范围(0~2V)。 七、 SignalTap II波形下图波形为利用Quartus II里面的工具SignalTap II采集的数据波形。 高速AD/DA实时采集回放实验(DA发生输出正弦波,AD实时采集) 实验视频地址:http://v.youku.com/v_show/id_XNDU5NTc4NjAw.html

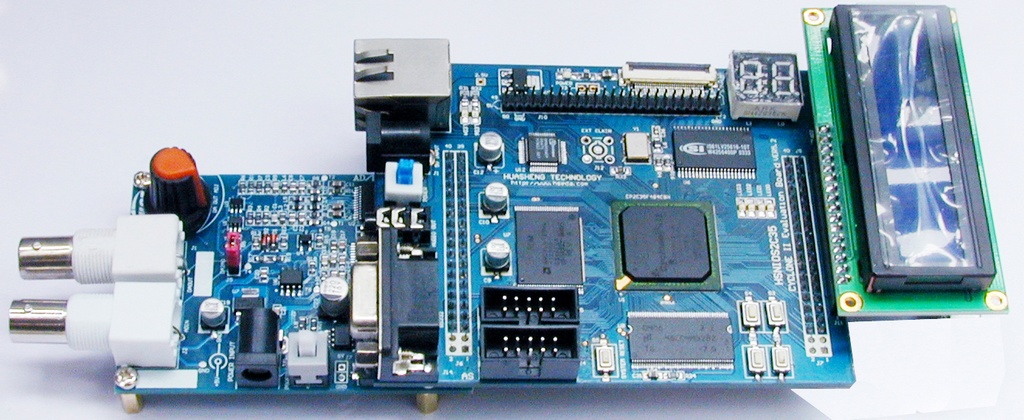

八、与我们常用核心板连接方法1.与FPGA核心板EP2C35连接图:扩展板要连接到FPGA2C35的J6位置,注意不要差错和插反方向。

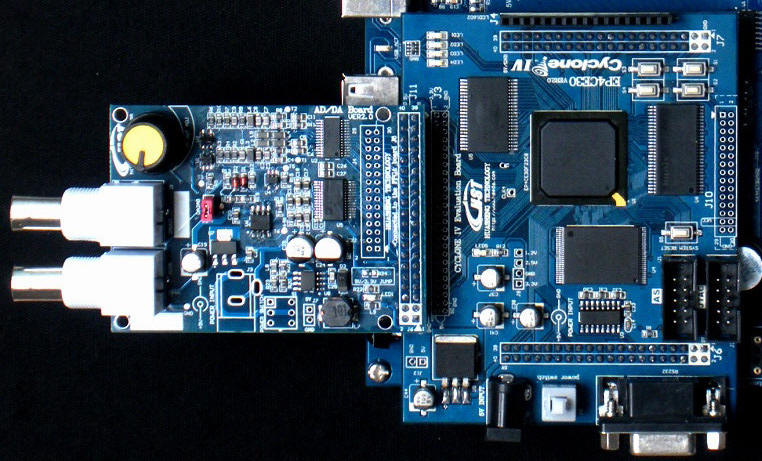

2:EP4CE30 VER2.0与ADDA VER2.0连接图

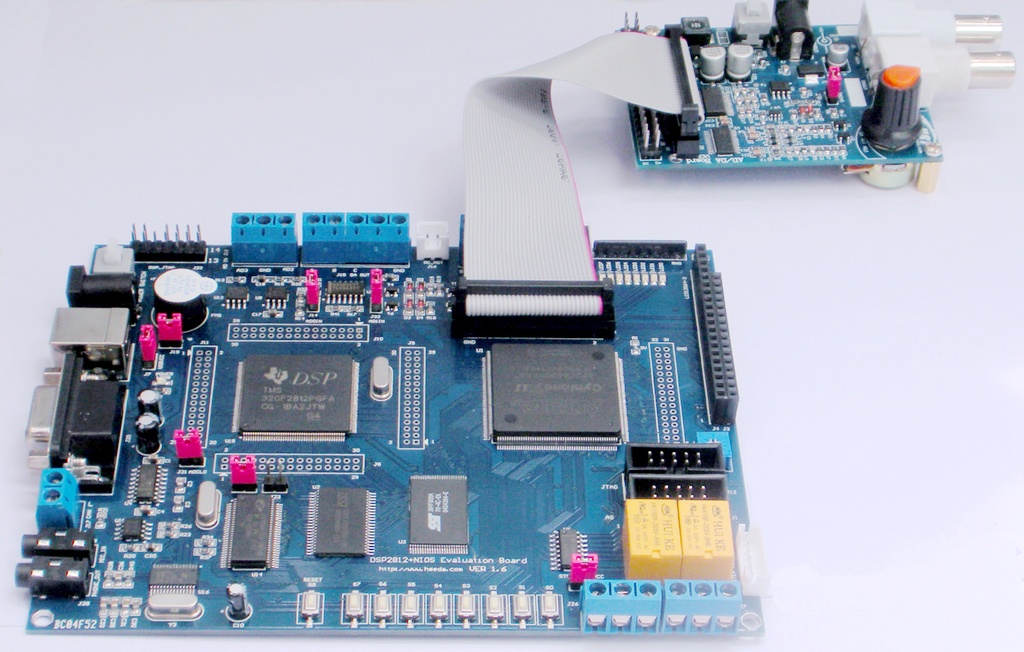

3.与DSP2812+FPGA连接图:扩展板通过我们的给的30PIN的软排线要连接到DSP2812+FPGA的J31位置,注意不要差错和插反方向。

|

||||||||||||||||||||||||||||||||||